SI5335D-B01740-GM QFN-24-EP 时钟发生器/频率合成器/PLL SILICON LABS 原装现货

说明

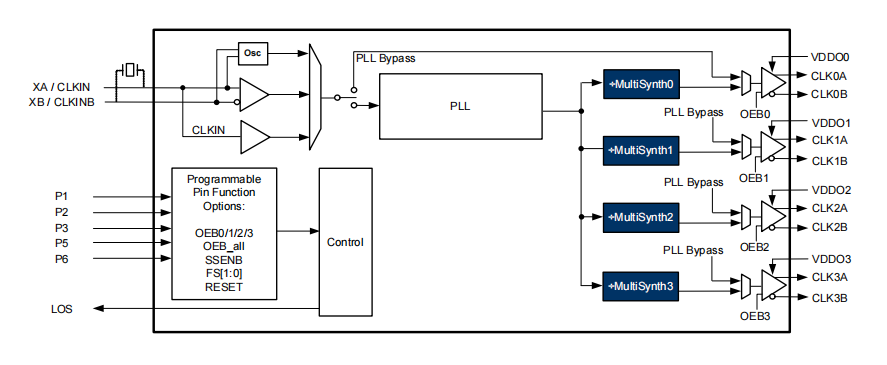

Si5335是一种高度灵活的时钟发生器,能够合成4个完全非整数相关的频率高达350 MHz。该设备有四组输出,每个组支持一个差分对或两个单端输出。使用硅实验室的专利多合成分数分频器技术,所有输出都保证有0 ppm的频率合成误差,无论配置如何,从而可以用一个设备替换多个时钟集成电路和晶体振荡器。

Si5335支持最多三种独立的、可通过引脚选择的设备配置,使一个设备可以取代三个独立的时钟发生器或缓冲集成电路。为了简化系统设计,最多提供了5个用户可分配和引脚可选择的控制引脚,支持pcie兼容的扩频控制、主和/或单独输出启用、频率计划选择和设备复位。

两个可选择的PLL环路带宽支持应用程序中的抖动衰减,如PCIe和DSL。通过其灵活的时钟建设者™(www.silabs.com/ClockBuilder)网络配置工具,工厂定制,引脚控制设备在两周内,没有最低订单数量限制。测量PCIe时钟抖动是快速和容易与硅实验室PCIe时钟抖动工具。

特征

低功耗MultiSynth™ 技术

启用独立的、任何频率

四个频率的合成

可配置为时钟发生器或

时钟缓冲装置

三种独立的、用户可指定的、引脚可选择的设备配置

具有高度可配置的输出驱动器

最多四个差分输出,八个

单端时钟输出,或

两者的结合

0.7 ps RMS的低相位抖动

灵活的输入参考:

外部晶体:25或27 MHz

CMOS输入:10至200 MHz

SSTL/HSTL输入:10至350 MHz

差分输入:10至350 MHz

可独立配置的输出

支持任何频率或格式:

LVPECL/LVDS/CML:1至350兆赫

HCSL:1至250兆赫

CMOS:1至200 MHz

SSTL/HSTL:1至350兆赫

每个驱动器的独立输出电压:

1.5、1.8、2.5或3.3伏

单芯供电,性能优异

PSRR:1.8、2.5、3.3伏

最多五个用户可分配引脚

功能简化了系统设计:

SSENB(扩频控制),

RESET、主OEB或每个引脚的OEB,

应用

以太网交换机/路由器

PCI Express第1/2/3/4代

PCIe抖动衰减

DSL抖动衰减

广播视频/音频定时

处理器和FPGA时钟

MSAN/DSLAM/PON公司

光纤通道、SAN

电信线路卡

1 GbE和10 GbE

原理框图